4.4 Транзистор-транзисторная логика (ТТЛ)

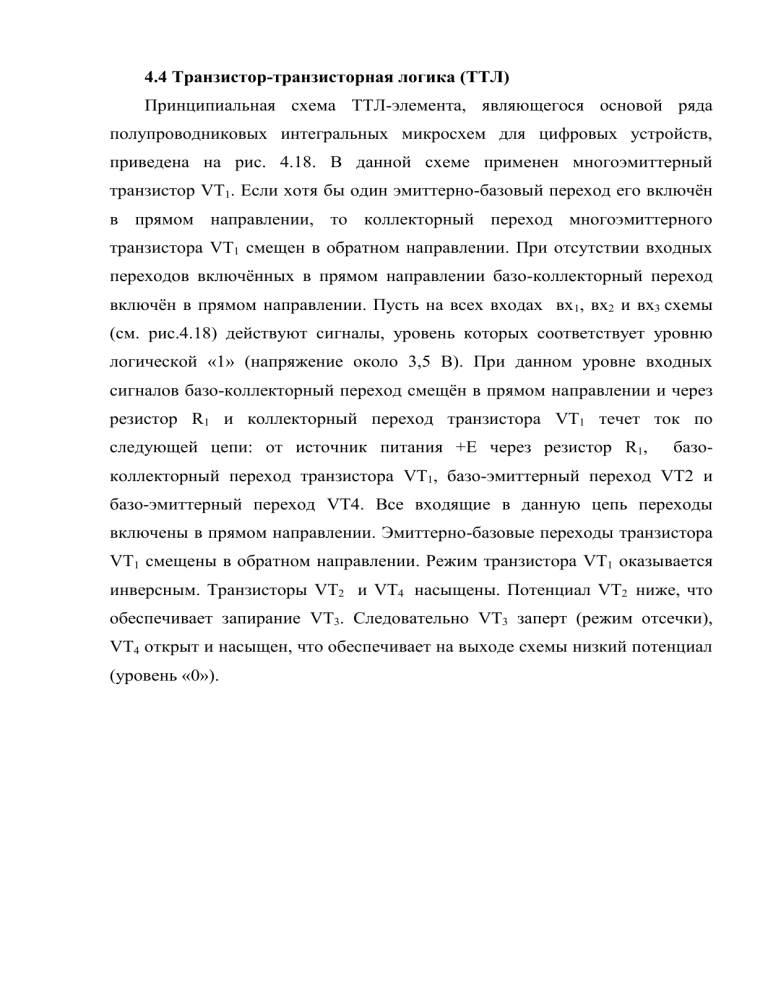

Принципиальная схема ТТЛ-элемента, являющегося основой ряда

полупроводниковых интегральных микросхем для цифровых устройств,

приведена на рис. 4.18. В данной схеме применен многоэмиттерный

транзистор VT1. Если хотя бы один эмиттерно-базовый переход его включён

в прямом направлении, то коллекторный переход многоэмиттерного

транзистора VT1 смещен в обратном направлении. При отсутствии входных

переходов включённых в прямом направлении базо-коллекторный переход

включён в прямом направлении. Пусть на всех входах вх1, вх2 и вх3 схемы

(см. рис.4.18) действуют сигналы, уровень которых соответствует уровню

логической «1» (напряжение около 3,5 В). При данном уровне входных

сигналов базо-коллекторный переход смещён в прямом направлении и через

резистор R1 и коллекторный переход транзистора VT1 течет ток по

следующей цепи: от источник питания +Е через резистор R1,

базо-

коллекторный переход транзистора VT1, базо-эмиттерный переход VT2 и

базо-эмиттерный переход VT4. Все входящие в данную цепь переходы

включены в прямом направлении. Эмиттерно-базовые переходы транзистора

VT1 смещены в обратном направлении. Режим транзистора VT1 оказывается

инверсным. Транзисторы VT2 и VT4 насыщены. Потенциал VT2 ниже, что

обеспечивает запирание VT3. Следовательно VT3 заперт (режим отсечки),

VT4 открыт и насыщен, что обеспечивает на выходе схемы низкий потенциал

(уровень «0»).

+E

R1

вх1

вх2

Rk

VT1

вх3

VT2

VT3

VD1

Uвых

VD2-VD4

VT4

Rэ

-E

Рис.4.18

При другом сочетании входных сигналов, когда хотя бы один из них

имеет низкий уровень напряжения – уровень логического «0» (примерно 0,3

В), тогда эмиттерно-базовый переход, соответствующего входа, смещен в

прямом направлении. Прямой ток этого перехода протекает по цепи,

включающей источник питания +Е, резистор R1, эмиттерно-базовый переход

и источник входного сигнала. Считая напряжение на эмиттерно-базовом

переходе, смещенном в прямом направлении, близким к 0,6 В, получим, что

напряжение на базе транзистора VT1 относительно корпуса равно 0,9 В

( U б U вх U бэ 0,3 0,6 0,9 В ).

Напряжение на коллекторе многоэмиттерного транзистора будет меньше

U б на значение падения напряжения на включенном коллекторном переходе

U кб , т.е. примерно 0,4 В, и составляет всего 0,5 В. Это напряжение меньше,

чем сумма напряжений отсечки

эоб 2 и эоб 4 . Входное сопротивление

выключенного транзистора VT2, составляющее коллекторную нагрузку

многоэмиттеного транзистора VT1, очень велико. Входным током запертого

транзистора VT2 служит малый ток I ко2 . Этот ток и является коллекторным

током транзистора VT1. Таким образом, транзистор VT1 имеет значительный

ток базы, протекающий через открытый базо-эмиттерный переход, и очень

малый коллекторный ток, равный I ко2 .

При таком соотношении базового и коллекторного токов транзистор VT1

насыщен; его коллекторный переход смещен в обратном направлении.

Эмиттерно-базовый ток, протекающий через открытый входной переход,

складывается из тока базы I б ( E Uб ) R1 и тока коллектора I ко2 . Значение

эмиттерного тока соответствует входному току элемента при наличии

напряжения уровня логического «0» на входе. Остальные эмиттеры VT1 попрежнему работают в инверсном режиме и ток их мал.

Таким образом, при напряжении соответствующем уровню логического

«0» хотя бы на одном из входов транзистор VT2 заперт. Потенциал

коллектора VT2 близок к +Е, что открываети насыщает VT3. При этом VT4

заперт, т.к. потенциал его базы близок к нулю. На выходе схемы при этом

имеет место высокое напряжение порядка 3,5В (уровень логической «1»), т.к.

+Е поступает на выход схемы через насыщенный транзистор VT3 и диод VD1

включённый в прямом направлении. Диоды VD2-VD4 выполняют защитные

функции микросхемы от отрицательных входных импульсов. Указанное

преобразование сигнала соответствует логической операции «И-НЕ»,

которую выполняет каскад на многоэмиттерном транзисторе VT1 операция

«И» инвертор, собранный на транзисторах VT2, VT3 и VT4 (операция «НЕ»).

Параметры схемы «И-НЕ» серии К155: U 0 0,2 0,3В ; U 1 3,5 4 В ;

0

1

I вх

0,3 мА ; I вх

мА ; Pпот 70 мВт ; tвкл 20 нс .

4.5 Логические элементы на МОП и КМОП-структурах.

Появление

и

широкое

использование

полевых

транзисторов

с

изолированным затвором положило начало ряду очень перспективных

семейств логических элементов.

В основе МДП-логики, или, что то же самое, МОП-логики (МОПТЛ),

ключевые схемы на МОП-транзисторах. В них за уровень логического нуля

принимается напряжение на открытом транзисторе, которое у полевых

транзисторов столь же мало, как у насыщенного биполярного транзистора,

т.е. 0,05-0,15 В. За уровень логической единицы принимают напряжение

сток-исток закрытого транзистора, которое близко к напряжению питания

схемы.

Таким

образом,

логический

перепад

напряжения

близок

к

напряжению питания.

Большая разница между уровнями нуля и единицы значительно

повышают помехоустойчивость схемы по сравнению с логикой на

биполярных элементах, такой как ДТЛ, ТТЛ и особенно ЭСТЛ, НСТЛ и И2Л.

Еще одно преимущество МОП-логики заключается в том, что ее

входные (затворные) цепи практически не потребляют тока. Влияние

входной цепи последующего (нагрузочного) элемента сводится лишь к

увеличению входной емкости данной ячейки.

Однако как раз это преимущество — высокое сопротивление входных

цепей — приводит к затягиванию заряда и разряда паразитных емкостей, что

является главной причиной невысокого быстродействия МОП-логики по

сравнению с ЭСТЛ, ТТЛ.

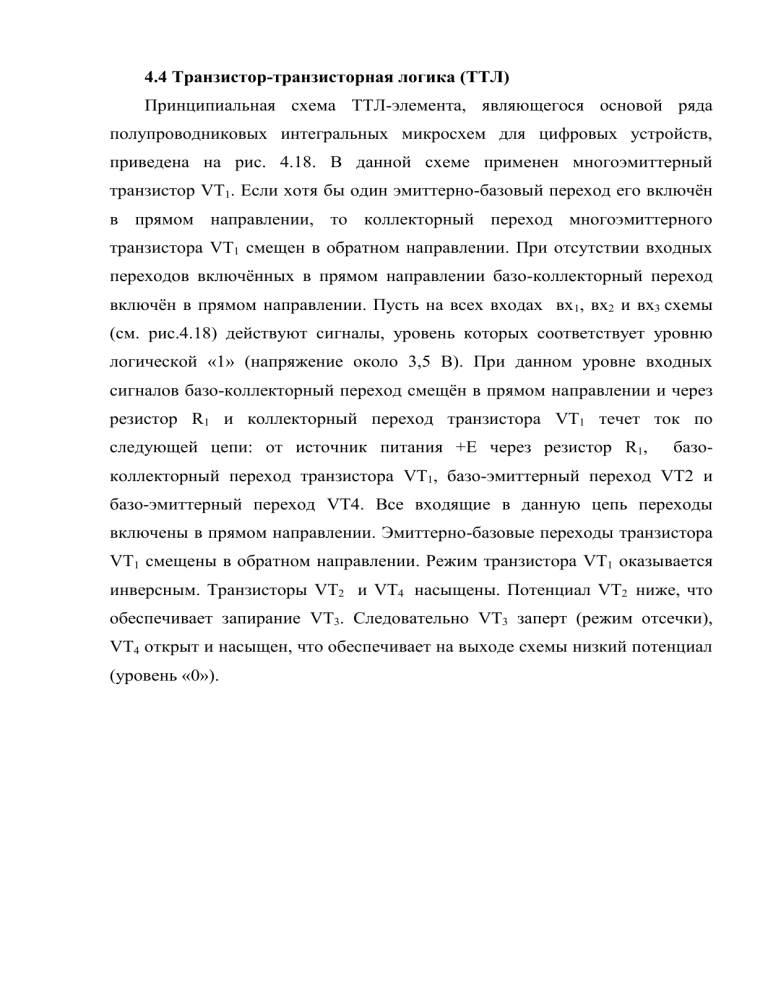

На рис. 4.19. а, б приведены ячейки типа ИЛИ-НЕ и И-НЕ,

реализованные на МОП-транзисторах с индуцированным n-каналом. Здесь

Транзистор Т3 служит динамической нагрузкой. В схеме на рис. 4.19, а

логические транзисторы Т1 и Т2 включены параллельно, поэтому отпирание

каждого из низ логической единицей на входе приводит к снижению

выходного уровня до логического нуля, т.е. схема выполняет операцию ИЛИНЕ.

В логической схеме на рис. 4.19, б ток в цепи, а значит, и низкий уровень

выходного напряжения возможен только при отпирании всех

(в данном

случае обоих) транзисторов. Это имеет место при подаче напряжения

высокого уровня, соответствующего логической единице, одновременно на

все входы. Отсюда ясно, что эта схема выполняет функцию И-НЕ.

+E0

+E0

T3

T3

y

y

x1

T1 x2

T2

C

x1

T2

x2

T1

б)

а)

+E0

T3

U'з-и

T3

T4

T4

T2

x1

T2

x2

+E0

y

y

T1

x1

U'з-и

Uз-и

x2

T1

Uз-и

г)

в)

Рисунок 4.19.

МОП-логика на ключах с динамической нагрузкой не получила

существенного распространения из-за заметного потребления энергии

ключом в открытом состоянии.

МОП-транзисторная

логика

на

комплиментарных

транзисторах

(КМОПТЛ) имеет основное достоинство в том, что в ней изменение

выходного напряжения не связано с изменением тока: он остается близким к

нулю. Два типовых варианта таких логических элементов показаны на рис.

4.19, в, г, из которых видна закономерность структуры КМОПТЛ:

параллельное

соединение

транзисторов

одного

типа

сопровождается

последовательным соединением транзисторов другого типа. Выполняемая

логическая функция определяется включением транзисторов «нижнего

этажа» Т1 и Т2. В рассматриваемой схеме это n-канальные транзисторы.

Если изменить полярность питающего напряжения, то в «нижнем этаже»

окажутся транзисторы с p-каналом.

Пусть в схеме на рис. 4.19, в на оба логических входа поданы уровни

x1=x2=Uз-и=0. Тогда в n-канальных транзисторах Т1 и Т2 канала не

образуется, т.е. они заперты. В p-канальных транзисторах Т3 и Т4, наоборот,

образуется каналы, так как разность потенциалов U’з-и Е0 заведомо

превышает (по модулю) пороговое напряжение. Однако поскольку через

каналы протекают ничтожно малые токи запертых транзисторов Т1 и Т2,

падение напряжения на каналах тоже получается ничтожным. Поэтому

можно считать, что выходное напряжение равно напряжению питания. Это и

есть уровень единицы (y=1).

Если поданы на входы x1 или x2 уровень Uз-и=Е0, то в транзисторе Т1

(Т2) образуется кал, а в транзисторе Т3(Т4) исчезает, т.е. этот транзистор

запирается. Ничтожно малый остаточный ток транзистора Т3 (Т4), протекая

через канал Т1 (Т2), дает на нем практически нулевое падение напряжения

(y=0).

Помимо

высокой

экономичности,

преимуществом

КМОПТЛ

по

сравнению с МОПТЛ являются малые рабочие напряжения и более высокое

быстродействие. Схема на рис 4.19, г характеризуется аналогичными

свойствами, какими пользовались выше.

ЛИТЕРАТУРА

1. Баскаков С.И. Радиотехнические цепи и сигналы Учебник для вузов.

- М. Высшая школа, 1988.

9. Даджион Д., Мерсеро Р. Цифровая обработка многомерных сигналов.

– М.: Мир, 1988. – 488 с.

10. Дмитриев В.И. Прикладная теория информации: Учебник для вузов.

- М.: Высшая школа, 1989.

14. Купер Дж., Макгиллем А. Вероятностные методы анализа сигналов

и систем. – М.: Мир, 1989.

15. Лосев А.К. Линейные радиотехнические цепи: Учебник для вузов. М.: Высшая школа, 1971.

18. Оппенгейм А.В., Шафер Р.В. Цифровая обработка сигналов. – М.:

Связь, 1979. – 416 с.

25. Сергиенко А.Б. Цифровая обработка сигналов. / Учебник для вузов.

– СПб.: Питер, 203. – 608 с