Лекция-5 Проектирования биполярных VLSI

3.3. Эмиттерно-связанная логика

Принцип работы. Построение схем

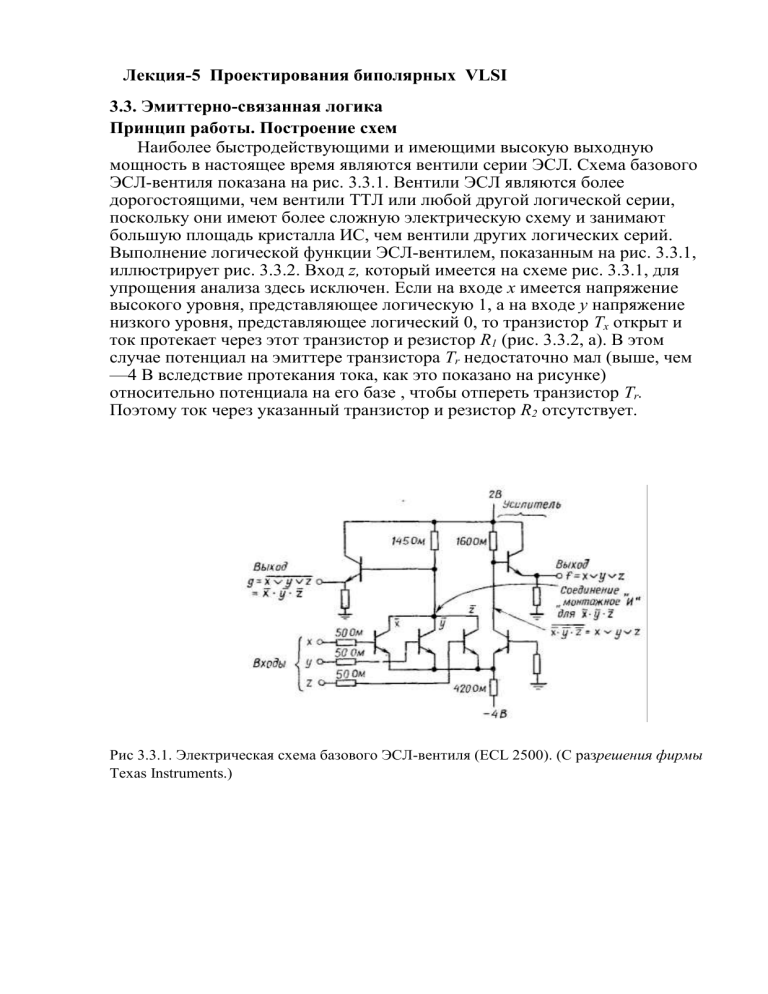

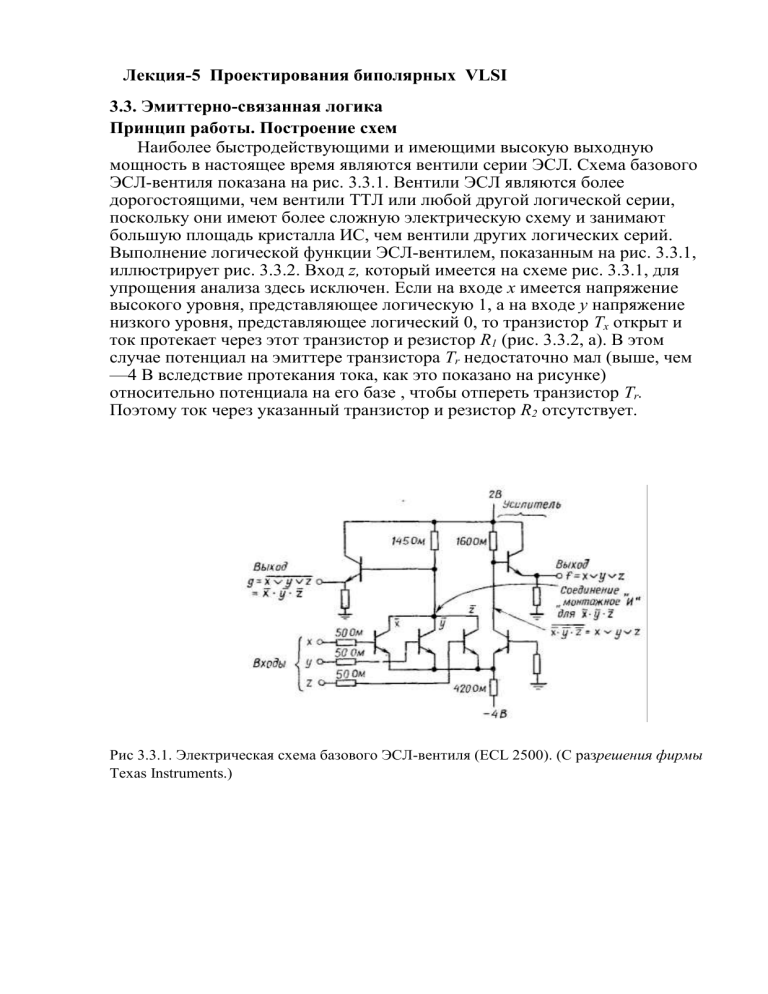

Наиболее быстродействующими и имеющими высокую выходную

мощность в настоящее время являются вентили серии ЭСЛ. Схема базового

ЭСЛ-вентиля показана на рис. 3.3.1. Вентили ЭСЛ являются более

дорогостоящими, чем вентили ТТЛ или любой другой логической серии,

поскольку они имеют более сложную электрическую схему и занимают

большую площадь кристалла ИС, чем вентили других логических серий.

Выполнение логической функции ЭСЛ-вентилем, показанным на рис. 3.3.1,

иллюстрирует рис. 3.3.2. Вход z, который имеется на схеме рис. 3.3.1, для

упрощения анализа здесь исключен. Если на входе х имеется напряжение

высокого уровня, представляющее логическую 1, а на входе у напряжение

низкого уровня, представляющее логический 0, то транзистор Тх открыт и

ток протекает через этот транзистор и резистор R1 (рис. 3.3.2, а). В этом

случае потенциал на эмиттере транзистора Тr недостаточно мал (выше, чем

—4 В вследствие протекания тока, как это показано на рисунке)

относительно потенциала на его базе , чтобы отпереть транзистор Тr.

Поэтому ток через указанный транзистор и резистор R2 отсутствует.

Рис 3.3.1. Электрическая схема базового ЭСЛ-вентиля (ECL 2500). (С разрешения фирмы

Texas Instruments.)

Следовательно , на базе транзистора Tf имеет место высокий

потенциал, который отпирает Tf, и на выход f поступает напряжение

высокого уровня, представляющее собой логическую 1. В то же время

транзистор Tg почти заперт (в действительности через него протекает

небольшой ток, которым для простоты можно пренебречь), так как его

база имеет низкий потенциал вследствие падения напряжения на

резисторе R1при протекании через него тока, как показано на рисунке.

Таким образом, на выходе g имеет место низкий потенциал,

соответствующий логическому 0.

Рис. 3.3.2. Логическая операция базового ЭСЛ-вентиля.

Если на вход у (вместо входа x) или на оба входа x и у подано

напряжение высокого уровня, рассмотренная выше ситуация не изменится,

за тем исключением что ток будет протекать через транзистор Тy или через

оба транзистора Тx и Тy.

Предположим теперь, что на оба входа x и y подано напряжение низкого

уровня (рис. 3.3.2,б). В этом случае ток через резистор отсутствует.

Поэтому, как показано на рис. 3.3.2, б, ток будет протекать через резистор R2

и транзистор Тr, так как база транзистора Тr имеет более высокий потенциал,

чем эмиттер (~0 В на базе и –0,8 В на эмиттере). Таким образом, на базе

транзистора T f образуется низкий потенциал и транзистор почти запирается

(говоря более точно, ток через транзистор Tf значительно уменьшается).

Следовательно, на выходе f имеет место напряжение низкого уровня,

соответствующее логическому 0. У транзистора Tg в этом случае на базе

высокий потенциал, и этот транзистор открывается. Таким образом, на

выходе g оказывается напряжение высокого уровня, соответствующее

логической 1.

Таблица 3.3.1. Таблица истинности для схемы,

приведенной на рис. 3.3.2

Входы

X

0

0

1

1

Выходы

y

0

1

0

1

f

0

1

1

1

g

1

0

0

0

Проведенный анализ схемы на рис. 3.3.2 позволяет составить

таблицу истинности (табл. 3.3.1) реализуемой ею функции. В

соответствии с этой таблицей схема имеет два выхода:

Аналогичным образом можно определить, что схема ЭСЛ-вентиля,

приведенного на рис. 3.3.1, имеет два выхода:

Условное обозначение такого вентиля показано на рис. 3.3.3. Благодаря

особенностям электрической схемы ЭСЛ-вентиля если на его выходе

реализована любая из функций

либо

,то обратная ей

функция может быть легко реализована путем добавления двух элементов:

транзистора и резистора. Возможность одновременного получения (при

использовании нескольких дополнительных компонентов на выходе ЭСЛвентиля) двух логических функций ИЛИ и ИЛИ-НЕ, т. е. парафазного

выходного сигнала, является уникальной особенностью, значительно

расширяющей возможности логического проектирования ЭСЛ-схем.

Рис 3.3.3. Условное обозначение ЭСЛ-вентиля, показанного на рис. 3.3.1.

Рис 3.3.4. Включение ЭСЛ-вентилей с помощью соединения «монтажное ИЛИ».

Другой важной особенностью ЭСЛ-вентиля является возможность

реализации операции «монтажное ИЛИ». Как показано на рис. 3.3.4,

логическая операция ИЛИ может быть выполнена без использования

дополнительного вентиля, простым соединением выходов вентилей. (Это

возможно потому, что выходы этих вентилей являются выходами

эмиттерных повторителей.) Такое соединение называется монтажное

ИЛИ, эмиттерное или имплицированное ИЛИ. Выполнение этого

соединения не требует никаких затрат, за исключением площади,

занимаемой им на кристалле. Оно является очень удобным при логическом

проектировании. Если выход одного ЭСЛ-вентиля соединен по схеме

«монтажное ИЛИ» с выходом другого, то он не обеспечивает

первоначальной функции и не может подаваться на вход других вентилей.

Рис. 3.3.5. Использование соединения «монтажное ИЛИ» для включения многовыходных

ЭСЛ-вентилей.

Однако если тот же самый выход дублируется внутри вентиля с помощью

дополнительной пары транзистор — резистор, то, как показано на рис. 3.3.5,

новый выход может быть соединен с выходом другого вентиля или с

входами следующих вентилей с использованием «монтажное ИЛИ».

Например, у

верхнего ЭСЛ-вентиля (рис. 3.3.5) первый выход

может быть

соединен с входами следующих вентилей, в то время как эта же функция

со второго выхода, соединенного по схеме «монтажное ИЛИ» с выходом

второго ЭСЛ-вентиля, создает выходной сигнал

.

Рис. 3.3.6, Переход от ЭСЛ-схемы к схеме на элементах ИЛИ-НЕ: а — ЭСЛ-схема; б —

схема на элементах ИЛИ-НЕ; в — ЭСЛ-схема с соединениями «монтажное ИЛИ»; г —

ЭСЛ-схема без соединений «монтажное ИЛИ».

Максимальный коэффициент разветвления по выходу для ЭСЛ-вентиля

лежит в диапазоне 10—25 в зависимости от требуемого быстродействия и

других условий.

Схемы из ЭСЛ-вентилей могут проектироваться на основе схем,

состоящих только из вентилей ИЛИ-НЕ. Причина этого заключается в

следующем. Рассмотрим схему из ЭСЛ-вентилей, изображенную на

рис.

3.3.6, а, на которой с целью упрощения не показано соединение

«монтажное ИЛИ». Эта схема может быть преобразована в схему,

приведенную на рис.

3.3.6, б, путем устранения выхода ИЛИ у левого вентиля (рис. 3.3.6, а) и

непосредственного подсоединения входов х и у этого вентиля к входам

правого вентиля. Таким образом, схема на рис. 3.3.6, б, на выходе которой

получается та же функция, что и у схемы на рис. 3.3.6, а, состоит только из

вентилей ИЛИ-НЕ; при этом количество входов правого вентиля

увеличилось, а сигналы х и y поступают на входы этого вентиля быстрее.

Следует подчеркнуть, что при таком преобразовании число вентилей не

изменится. В случае если схема из ЭСЛ-вентилей содержит соединения

«монтажное ИЛИ», она может быть приведена к схеме из вентилей ИЛИ-НЕ

таким же образом. Например, схема на рис. 3.3.6, в с соединениями

«монтажное ИЛИ» может быть преобразована в схему, не содержащую таких

соединений (рис. 3.3.6, г). При этом увеличивается количество входов

некоторых вентилей. Заметим, что два выхода ИЛИ-НЕ левого верхнего

вентиля (рис. 3.3.6, в) могут быть объединены в один (рис. 3.3.6,г). Поэтому

можно применять вышеприведенное преобразование с целью получения

схемы на вентилях ИЛИ-НЕ с тем же количеством вентилей и, возможно,

увеличенным для некоторых вентилей количеством входов. Ситуация не

изменяется и в том случае, если каждый вентиль имеет более двух выходов

ИЛИ-НЕ или ИЛИ.

Любая более сложная, чем в рассмотренных примерах, ЭСЛ-схема может

быть подобным образом преобразована в схему, состоящую только из

вентилей ИЛИ-НЕ.

Если необходимо разработать схему из ЭСЛ-вентилей для заданных

функций f и f, то ее проектирование можно осуществлять на основе схемы

из вентилей ИЛИ-НЕ, как это показано ниже, посредством преобразования,

обратного ранее рассмотренному.

Процедура 3.3.1. Проектирование логических схем на ЭСЛ-вентилях

1. Разработайте логические схемы для функций fи , используя только

вентили ИЛИ-НЕ и не учитывая ограничения по количеству входов и по

нагрузочной способности. Количество вентилей в каждой схеме должно

быть минимальным.

2. Выберите из полученных двух логических схем схему с минимальным

количеством вентилей. Если возможно, сократите число входов каждого

вентиля, пользуясь соединением «монтажное ИЛИ» или выходами ИЛИ

других вентилей. В случае необходимости следует предусмотреть

дополнительные выходы ИЛИ-НЕ и ИЛИ вентилей (см. рис. 3.3.5). Когда

максимально возможное число входов какого-либо вентиля оказывается

превышено, этого можно избежать, используя соединения «монтажное ИЛИ»

или выходы ИЛИ.

3. Обычно в ходе выполнения этой процедуры уменьшается также и

число нагрузок на выходах вентилей. Однако, если у некоторых вентилей

нагрузочный коэффициент по выходу все-таки превышает максимально

допустимый, устранить такую ситуацию можно, используя

дополнительные ЭСЛ-вентили. Выходной ЭСЛ-вентиль полученной

логической схемы вырабатывает заданные функции f и .

Если ни у одного вентиля в схеме после шага 2 не превышено допустимое

число нагрузок по выходу, то в полученной схеме количество ЭСЛ-вентилей

равняется числу вентилей ИЛИ-НЕ исходной схемы. Следовательно, когда

имеется исходная схема с минимальным количеством вентилей ИЛИ-НЕ, то

полученная схема также будет иметь минимальное количество ЭСЛвентилей в случае, если не потребуется вводить дополнительных вентилей на

шаге 3.

Отметим, что использование выходов ИЛИ и соединений «монтажное

ИЛИ» обычно уменьшает число связей между вентилями и, следовательно,

число соединений, подключаемых к входам вентилей, т. е. число входных

транзисторов. Тем самым также уменьшается общая длина соединений и

экономится площадь кристалла, занимаемая ими.

Логическое проектирование ЭСЛ-схем на схемном уровне

До настоящего момента мы рассматривали логическое проектирование

схем с использованием отдельных ЭСЛ-вентилей. Важной особенностью

ЭСЛ-схем является то, что, соединяя точки электрической схемы одного

ЭСЛ-вентиля с некоторыми точками на схеме другого ЭСЛ-вентиля, можно

реализовать сложную логическую функцию. При этом полученная

электрическая схема будет проще схемы, которая разрабатывается на основе

логической схемы из ЭСЛ-вентилей. Другими словами, можно реализовать

логические функции путем соединения транзисторов, резисторов и диодов

ЭСЛ-схем, вместо того чтобы использовать для достижения этой цели

электрические схемы логических вентилей с постоянной структурой. Такой

подход может быть назван схемным подходом к логическому

проектированию.

Рис. 3.3.7. Пример соединения «монтажное И»: а — электрические схемы двух ЭСЛвентилей; б — реализация логической функции

на схемном уровне логического

проектирования; в — реализация функции

с использованием схемы с

ЭСЛ-вентилями.

Рассмотрим электрические схемы двух ЭСЛ-вентилей (рис. 3.3.7, a).

Точка А или В схемы вентиля 1 может быть соединена с точками А' или В'

схемы вентиля 2. Такое соединение называется монтажное И или

коллекторное. Заметим, что сигнал в точке А соответствует функции

,

потому что напряжение становится высоким и представляет логическую 1

только в том случае, когда на оба входа x и у подано напряжение низкого

уровня, представляющее логический 0. Сигнал в точке В представляет

функцию

, поскольку напряжение в точке В является высоким или

низким в зависимости от того, какое напряжение — низкое или

высокое имеется в точке А.

Соединяя два ЭСЛ-вентиля, как показано на рис. 3.3.7, б, можно

реализовать функцию

. Полученная электрическая схема имеет

гораздо более простой вид, чем в случае ее построения в виде логической

схемы из ЭСЛ-вентилей, при котором требуется использовать четыре ЭСЛвентиля (рис. 3.3.7,в). Другими словами, логические произведения

и

получают с помощью соединения «монтажное И», а затем используют

соединение «монтажное ИЛИ» для реализации функции

. В этом

случае для улучшения работы электрической схемы могут понадобиться

некоторые резисторы или транзисторы. Например, через резисторы R1 и R2

на схеме вентиля 1 (рис. 3.3.7, а) протекает слишком большой ток, поэтому

для стабилизации тока на схеме рис. 3.3.7, б включены дополнительные

резисторы. Ненужные резисторы или транзисторы следует исключать из

электрической схемы.

Рис. 3.3.8. Последовательное соединение транзисторов. (MECL System Handbook, 1980. С

разрешения фирмы Motorola Semiconductor Products, Inc.)

Другим подходом к реализации логических функций является

последовательное соединение транзисторов в ЭСЛ-вентиле. Такое

соединение называется транзисторно-последовательным; иногда его

называют также «монтажное И», хотя в действительности оно реализует

функцию «монтажное ИЛИ». Транзисторы Т1 и T2 (рис. 3.3.8) соединены

последовательно. Такое соединение реализует операции

или

,

поскольку закономерности изменения напряжений на коллекторах

транзисторов соответствуют операциям и . Поэтому такое

последовательное соединение выглядит как последовательное

соединение контактов реле.

Более сложным примером использования такого соединения является

схема одноразрядного сумматора с тремя входами (полного сумматора) на

рис. 3.3.9. Обычно последовательно соединяют не более трех транзисторов

(два транзистора в нижней части схемы рис. 3.3.9 входят в цепь питания), так

как при слишком большом количестве транзисторов, включенных

последовательно, быстродействие вентиля снижается (вследствие появления

паразитных емкостей в пластине ИС). Транзистор T1, у которого напряжение

сигнала на коллекторе представляет собой операцию (поскольку равняется

логическому 0 когда B = 1, т. е. сигнал инвертируется), соединен

последовательно с расположенным рядом транзистором Т2. Напряжение

сигнала на коллекторе транзистора Т2 представляет логическую функцию

(AВ инвертируется вследствие того, что напряжение сигнала на коллекторе

является логическим 0 только в случае, когда А = B=1). Затем транзистор Т2

соединяется последовательно с транзистором Т3, у которого напряжение

сигнала на коллекторе представляет логическую функцию ABC. Операция

«монтажное И» реализуется параллельным соединением транзисторов, у

которых напряжения сигналов на коллекторах представляют логические

функции

,

,

и

. С помощью операции «монтажное И»

формируется инверсное значение суммы, т. е.

. (Соединение такого

типа ранее уже использовалось для входов на схеме рис. 3.3.1. Другими

словами, выходной сигнал элемента ИЛИ-НЕ на схеме рис. 3.3.1

соответствует операции «монтажное И» над сигналами , и , т. е.

.) Обычно параллельно соединяют не более

восьми транзисторов.

Следует подчеркнуть, что коллекторное и транзисторнопоследовательное соединения возможны только в том случае, когда ЭСЛсхема реализуется в одном кристалле. Если каждый ЭСЛ-вентиль

реализуется отдельной ИС с дополнительными контактами для внешних

связей, такие соединения невозможны без ухудшения быстродействия ЭСЛсхемы. Операция «монтажное И» вместе с операцией «монтажное ИЛИ» и

наличием у вентилей выходов ИЛИ и ИЛИ-НЕ делают логическое

проектирование схем с ЭСЛ-вентилями очень гибким. Вследствие этого

ЭСЛ-схемы, при разработке которых используются не только отдельные

вентили, могут быть более быстродействующими и иметь более простую

электрическую схему, чем схемы с ЭСЛ-вентилями, в которых вентили

рассматриваются как независимые целостные строительные блоки. Тем не

менее, даже в случае, когда схема реализуется на ЭСЛ-вентилях, она обычно

содержит меньше ЭСЛ-вентилей и логических уровней, чем когда она

разрабатывается с использованием только вентилей ИЛИ-НЕ, так как каждый

ЭСЛ-вентиль имеет парафазные выходы ИЛИ-НЕ и ИЛИ.

Рис. 3 4.9. ECL-схема полного сумматора; буквы рядом с транзисторами отображают переключательные функции. (Патент фирмы

Motorola; Spectrum, р. 34 (Dec. 1970); Copyright © 1970 IEEE.)

Эта особенность ЭСЛ-вентилей позволяет еще более увеличивать

быстродействие ЭСЛ-схем. Принято считать, что быстродействие ЭСЛ-схемы в

среднем в ~1,5 раза больше, чем у схемы, реализованной только на вентилях

ИЛИ-НЕ. В этом смысле лучшие результаты логического проектирования

достигаются не за счет работы с отдельными вентилями, а благодаря

относительно более свободному соединению транзисторов.

ЭСЛ позволяет свободно использовать логическое проектирование на

схемном уровне, так как ЭСЛ-схема является таким же переключателем

тока, как реле. В этом смысле элемент ЭСЛ сочетает в себе качества

электронного вентиля и реле.

Таким образом, логическое проектирование ЭСЛ-схем

выполняется следующим образом.

1. Логическое проектирование на уровне вентилей. Каждый ЭСЛвентиль рассматривается как независимый от других вентилей строительный

блок, внутренняя схема которого не должна претерпевать изменения.

Логическая схема разрабатывается на основе ЭСЛ-вентилей, которые имеют

парафазные выходные сигналы ИЛИ-НЕ и ИЛИ (в ИС некоторых серий

каждый из этих выходных сигналов может быть дублирован); возможно

использование соединения «монтажное ИЛИ».

2. Логическое проектирование на схемном уровне. ЭСЛ-схема

разрабатывается на основе соединений, реализуемых на уровне

электрических схем ЭСЛ-вентилей:

а) соединение «монтажное И» — коллекторное соединение

(допустимо параллельное соединение не более восьми транзисторов) ;

б) соединение «монтажное ИЛИ» — эмиттерное соединение и

транзисторно-последовательное соединение (возможно

последовательное соединение не более трех транзисторов).

Проблемы использования ЭСЛ-схем

Схемы ЭСЛ имеют ряд недостатков. Одним из них является большая

потребляемая мощность. Так, ЭСЛ-вентиль потребляет от 20 до 60 мВт, в то

время как ТТЛ-вентиль — от 1 до 20 мВт. Вследствие этого при

использовании схем ЭСЛ не может быть достигнута столь высокая степень

интеграции БИС, как при использовании МОП-структур. В одном кристалле

может размещаться не более нескольких сотен ЭСЛ-вентилей в зависимости от

требуемого быстродействия и потребляемой мощности.

Вторым недостатком схем ЭСЛ является сложность выполнения

монтажных соединений, поскольку проводники печатной платы выполняют

роль передающих линий связи и форма сигналов существенно искажается, если

не предусмотреть соответствующих нагрузок на конце линий

Третьим недостатком является то, что для работы ЭСЛ-схемы необходимы

два источника питания.

Хотя для ЭСЛ-вентилей требуется большая площадь кристалла и они

потребляют значительную мощность, тем не менее эти схемы являются

самыми быстродействующими среди всех широко используемых типов

логических

схем. При этом ЭСЛ-схемы сохраняют работоспособность в большом

интервале температур и при колебаниях напряжения в цепях

питания.

Проблема теплового рассеяния

Поскольку многие компоненты ИС размещаются в очень небольшом

пространстве и при прохождении электрического тока выделяют тепло,

охлаждение этих компонентов представляет непростую задачу в связи с тем,

что охлаждать тело тем легче, чем больше его площадь. Некоторые

компоненты выделяют больше тепла, чем другие. Если несколько таких

компонентов ИС расположены близко друг от друга, то температура в этом

месте может сильно повыситься и привести к повреждению этих компонентов.

Поэтому в подобных случаях важной является задача такого размещения

компонентов, при котором обеспечивается равномерное распределение по

площади ИС выделяемого ими тепла. Эта задача важна еще и потому, что

количество тепла, выделяемое на единицу площади ИС, может быть велико,

хотя общее количество рассеиваемой мощности может быть незначительное.

Тепловую проводимость между кристаллом и корпусом ИС следует тщательно

учитывать при проектировании.

ЭСЛ с улучшенной изоляцией

Изопланарный процесс, рассмотренный в разд. 3.2, основное отличие

которого от планарной технологии состоит в замене диффузии p- типа для

создания изолирующей области на формирование изолирующего слоя

двуокиси кремния, начал применяться при изготовлении ЭСЛ-схем раньше,

чем для ТТЛ-схем.

Рис. 3.3.10 иллюстрирует совершенствование биполярного транзистора при

переходе от планарной технологии (рис 3.3.10, а) к изопланарной (рис. 3.3.10,

б), а затем к технологии «Изопланар II» (рис. 3.3.10, в). Об уменьшении

геометрических размеров транзистора при смене технологии дает

представление рис. 3.3.11. Благодаря использованию технологии «Изопланар

II» площадь транзистора уменьшилась более чем на 70% по сравнению с

площадью обычного планарного транзистора и более чем на 40% по

сравнению

с изопланарным транзистором. Дальнейшее уменьшение размеров было

достигнуто в 1979 г. при использовании технологии «Изопланар S». При этом

время задержки на один вентиль ЭСЛ уменьшилось с 500—700 пс для

технологии «Изопланар П» до 300—400 пс для технологии «Изопланар S».

Кроме того, благодаря уменьшению мощности рассеяния, достигнутому при

использовании изопланарной технологии, в одном кристалле может теперь

размещаться 1500 ЭСЛ-вентилей.

3.3.10. Сравнение структур биполярных транзисторов, полученных в процессе

совершенствования изопланарной технологии: а — планарная технология, 6

— изопланарная технология; в — технология «Изопланар II».

Рис. 3.3.11. Изменение топологии биполярного транзистора при совершенствовании

изопланарной технологии [Перепечатано из Electronics, p. 139 (Dec. 6, 1979). Copyright ©

McGraw-Hill, Inc., 1979. All rights reserved.]

В

1971 г. в изопланарной технологии применялась окисная изоляция. В

1975 г. при использовании технологии «Изопланар II» слой эмиттера был

расширен вплоть до изолирующих стенок, что позволило на 50% уменьшить

занимаемую площадь кристалла. В 1979 г. благодаря технологии «Изопланар

S» было достигнуто уменьшение геометрических размеров компонентов

транзистора.

На основе технологии « Изопланар II» фирма Fairchild разработала ИС на

ЭСЛ-схемах серии 100К. В случае МИС временная задержка на вентиль

составляет 750 пс при мощности рассеяния 40 мВт и нагрузке 50 Ом. Для СИС

временная задержка для внутренних вентилей ИС составляет менее 500 пс

при10 мВт. Серия 100К включает также ИС на ЭСЛ-вентилях, разработанные

на основе технологии «Изопланар S» временная задержка последних равна 400

пс.

Технологический процесс MOSAIC (Motorola oxide-isolated self-aligned

implanted circuit – технология ионно-имплантированных биполярных ИС с

оксидной изоляцией фирмы " Motorola") уменьшил типичное время задержки

с

2 нc (серия 10К) до 1 нc (серия 10КН) без увеличения потребляемой мощности.

На основе этого же процесса фирма разработала макроячеечную матрицу серии

MECL 10 000, в одном кристалле которой размещается 750 эквивалентных

вентилей.

На рис. 3.3.12 приведено сравнение параметров ИС серии ЭСЛ 100К,

изготовленной по изопланарной технологии, с другими типами логических ИС.

Рис. 3.3.12. Сравнение типов логических схем по критерию «произведение

временная задержка — мощность».

Наряду с использованием в ТТЛ- и ЭСЛ-схемах изопланарная

технология может также применяться для улучшения характеристик КМОПсхем. В частности, хорошие результаты дает ее использование для схем

памяти.

Правила разработки топологии ИС

К настоящему моменту сформулирован набор правил разработки

топологии биполярных транзисторных схем. А так как все эти правила должны

быть удовлетворены одновременно, проектирование топологии ИС является

сложной задачей, требующей больших затрат времени для решения. Ниже

приведены лишь наиболее общие правила разработки топологии ИС.

1. Биполярные транзисторы могут иметь различную топологию. Если

предполагается протекание большого тока в транзисторе, то добиться

однородного протекания тока можно, используя различную конфигурацию

транзистора (рис. 3.3.13). В каждом из приведенных вариантов топологии

коллектор, база и эмиттер могут быть разделены на несколько электродов,

соединенных металлическими полосками. При любой конфигурации

имеется один общий скрытый слой. Следует заметить, что транзисторы с

различной топологией имеют разные схемные параметры.

Рис. 3.3.13. Различные конфигурации топологии биполярного транзистора.

2. Изолирующие стенки ячеек, в которых расположены биполярные

транзисторы, могут быть общими. В случае, когда две изолирующие стенки

примыкают друг к другу (рис. 3.3.14, а), они могут быть объединены в одну

общую. Ширина стенки составляет не менее 10 мкм. На все изолирующие

стенки через пластину должен подаваться максимальный отрицательный

потенциал от источника питания.

Рис. 3.3.14. Изолирующие стенки

3. Транзисторы, коллекторы которых непосредственно соединены (рис.

3.3.15, а), могут быть реализованы с использованием одного скрытого слоя в

качестве общего коллектора. Как показано на рис. 3.3.15,б, эти транзисторы

могут размещаться в одной ячейке. Транзисторы, которые не имеют между

собой соединений, редко размещаются в одной ячейке. Причина этого

заключается в том, что если транзисторы размещаются в одной ячейке, то

они соединяются эпитаксиальным слоем n-типа.

Рис. 3.3.15. Транзисторы с соединенными коллекторами.

4. Расстояние между диффузионным базовым слоем и контактом коллектора

может быть увеличено, чтобы пропустить металлическое соединение (одну или

две металлические полоски) между контактами коллектора и базы. (Это можно

сделать, так как ток база — коллектор протекает главным образом между

диффузионным базовым слоем и скрытым слоем.) Однако чем больше

расстояние между базой и коллектором, тем больше паразитное сопротивление

и паразитная емкость коллектора. Металлический проводник не может

быть размещен между контактами базы и эмиттера за счет удлинения

диффузионного базового слоя.

5. Все транзисторы (а также и диоды, которые изготовляются вместе с

транзисторами), имеющие сходные схемные параметры, например паразитное

сопротивление и коэффициент усиления, следует ориентировать в одном

направлении для того, чтобы возможные незначительные смещения масок

одинаково сказывались на параметрах всех транзисторов. Другими словами,

если в одном транзисторе эмиттер находится к востоку от базы, то в другом

транзисторе он должен находиться тоже к востоку от базы (рис. 3.3.16).

Рис. 3.3.16. Взаимное расположение транзисторов.

6. Резисторы чаще всего реализуются в диффузионной области базы —

диффузионном базовом слое (рис. 3.3.17). Такой резистор изготавливается

одновременно с изготовлением баз транзисторов. Другими вариантами

реализации резисторов являются использование поликремниевой полоски

поверх слоя двуокиси кремния, а также применение скрытых областей базы

или коллектора, тонких пленок и диффузионных областей эмиттера или

коллектора.

Рис. 3.3.17. Структура резистора в диффузионной области базы.

Металлические соединения могут пересекаться с резисторами. Следует

заметить, что три слоя диффузионного базового резистора (рис. 3.3.17)

практически образуют паразитный р— п — р-транзистор (рис. 3.3.18),

коллектором которого является пластина p -типа (рис. 3.3.17). Для того чтобы

предотвратить отрицательное влияние р— п — р-транзистора (т. е. для

создания условий, при которых он всегда заперт ), потенциал среднего nслоя, который формируется напряжением ЕК , должен быть выше, чем

потенциал р-области, с тем чтобы оба диода (р — n-перехода в паразитном

транзисторе) были смещены в обратном направлении. Два верхних слоя (рис.

3.3.17), образующих диод, смещенный в обратном направлении, создают

также паразитную емкость.

Рис. 3.3.18. Паразитный транзистор в структуре резистора, реализованного в

диффузионной области базы.

7. Чтобы свести к минимуму отклонение величины сопротивления

резистора, являющееся следствием смещения масок, выводы резистора следует

располагать с противоположных сторон по отношению к резистору, как

показано на рис. 3.3.19.

Рис. 3.3.19. Конфигурация резистора.

8. Все резисторы должны размещаться в одной и той же ячейке и

реализовываться в одном большом скрытом слое. Резисторы также могут

группироваться отдельно, и каждая группа должна размещаться в своей ячейке.

9. В случае когда наличие паразитной емкости не существенно, резисторы

могут быть размещены в тех же ячейках, что и транзисторы, и реализованы в

общем с транзисторами скрытом слое. При этом не имеет значения, должны

ли они соединяться между собой. Расстояние между резисторами должно быть

не

менее 10 мкм. Коллектор транзистора и резистор должны располагаться

на расстоянии не менее 12 мкм.

10. В случае если изолирующая стенка является очень широкой, то

проходящая поверх нее полоска металлического соединения может

создавать большую паразитную емкость. Обычно эту емкость во внимание

не принимают.

11. Диоды, как правило, выполняются таким образом, что соединенные

вместе коллектор и база транзистора представляют собой один вывод диода, в

то время как эмиттер транзистора является его другим выводом.

12. Пересечение соединений выполняется согласно рис. 3.3.20. При этом,

так как диффузия n+-слоя может производиться одновременно с эмиттерной

диффузией, дополнительных технологических этапов при его изготовлении не

требуется. Пересечение точно таким же образом может выполняться и в

случае диффузионного базового резистора, показанного на рис. 3.3.17. Для

этого второе соединение должно размещаться между двумя выводами первого

перпендикулярно к соединяющей их линии и реализовываться в скрытом n+слое. Можно обойтись без использования скрытого слоя, если паразитный

транзисторный эффект является незначительным. В случае когда необходимо

наличие резистора в каком-нибудь соединении, удобно использовать резистор,

изображенный на рис. 3.3.17.

Рис. 3.3.20. Пересечение соединений.

Как правило, пересечение вносит дополнительное сопротивление. Поэтому

в цепях питания и заземления пересечений следует избегать. Поскольку

пересечения нежелательны также и в других случаях, следует уменьшить их

количество, насколько это возможно, путем перекомпоновки электрических

схем.

13. Большой скрытый слой в транзисторе или диоде образует значительную

паразитную емкость. Для быстродействующих вентилей, например ЭСЛвентилей, уменьшение паразитной емкости очень важно для повышения

быстродействия.